Dès son installation l'interface GUSTARD U16 a fait faire un bond en avant à mon système . Une électronique bien faite dans un boîtier à la finition exemplaire, une connectique complète et de qualité. Tout ça pour une musicalité pur plaisir. Prix très contenu, comme toujours avec AUDIOPHONICS. Bravo!

New Customer?

Create your accountNo products

Prices are tax included

GUSTARD U16 USB Digital Interface ES8620 SPDIF AES/EBU I2S HDMI LVDS Accusilicon 32bit 384kHz DSD512

By buying this product you get 30 loyalty points

This product has been replaced by the new version, the digital interface GUSTARD U18 USB XMOS XU216.

Gustard U16

USB Digital Interface ES8620 SPDIF AES/EBU I2S HDMI LVDS Accusilicon 32bit 384kHz DSD512

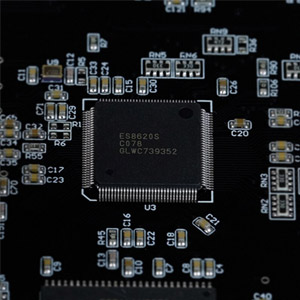

ES8620 USB Interface

Based on ESS' latest USB interface, the ES8620, the Gustard U16 digital interface is capable of supporting high sampling rates up to 32bit 768kHz for PCM and up to DSD512. Its rigorous and intelligent design allows it to offer excellent audio performance in terms of accuracy, message richness and dynamics. The entire architecture of the device is optimized to ensure the best possible digital signal processing.

Buffer & FPGA

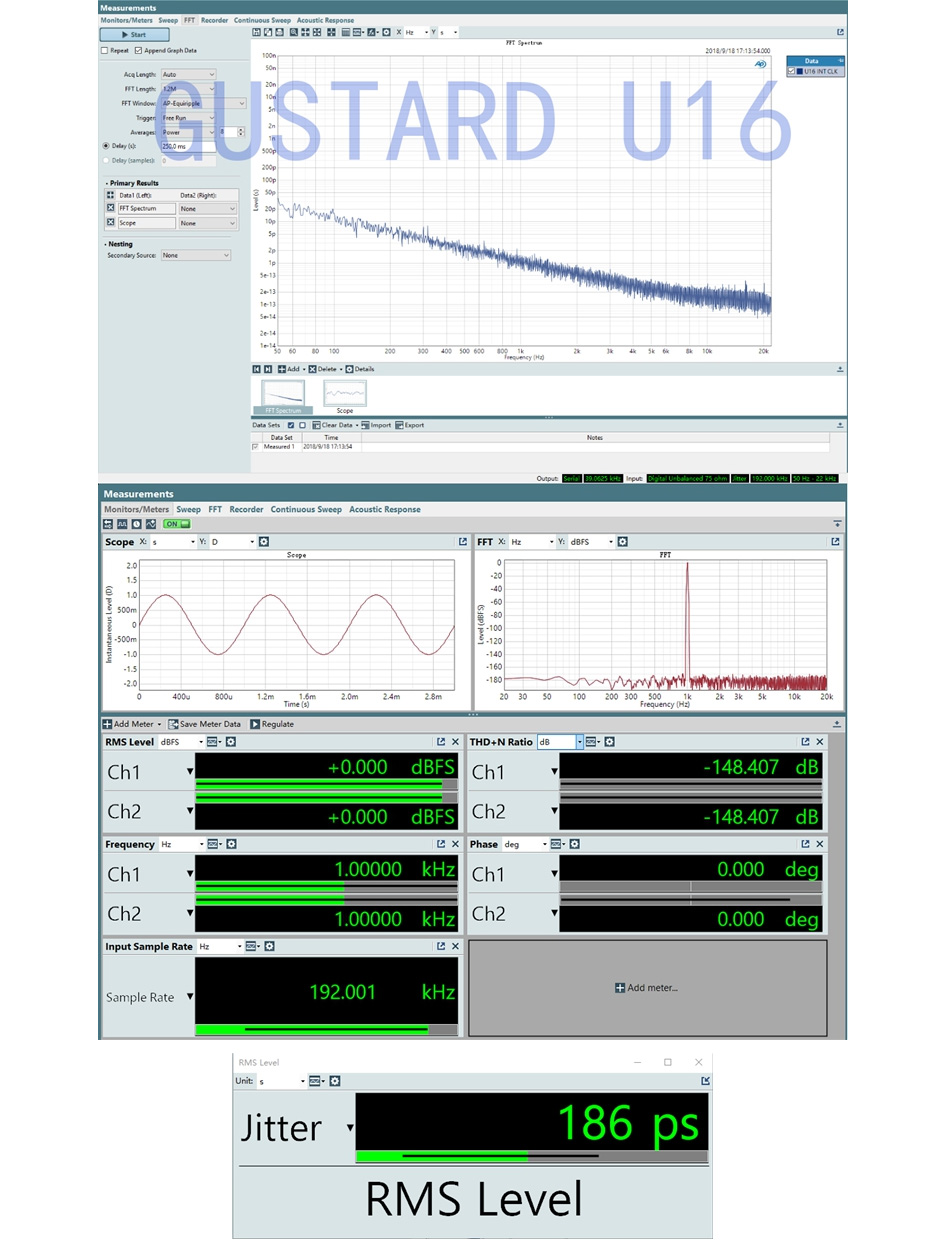

The Gustard U16 uses 128Mb of RAM as a system buffer and FIFO for processing digital audio signals. Most of the space is used for internal planning of the USB interface chip. The remaining space is reserved so that other logical operations do not interfere with the digital audio processing flow. In order to achieve optimal sound performance, the FIFO's capacity is reduced to a minimum to limit the delay and jitter.

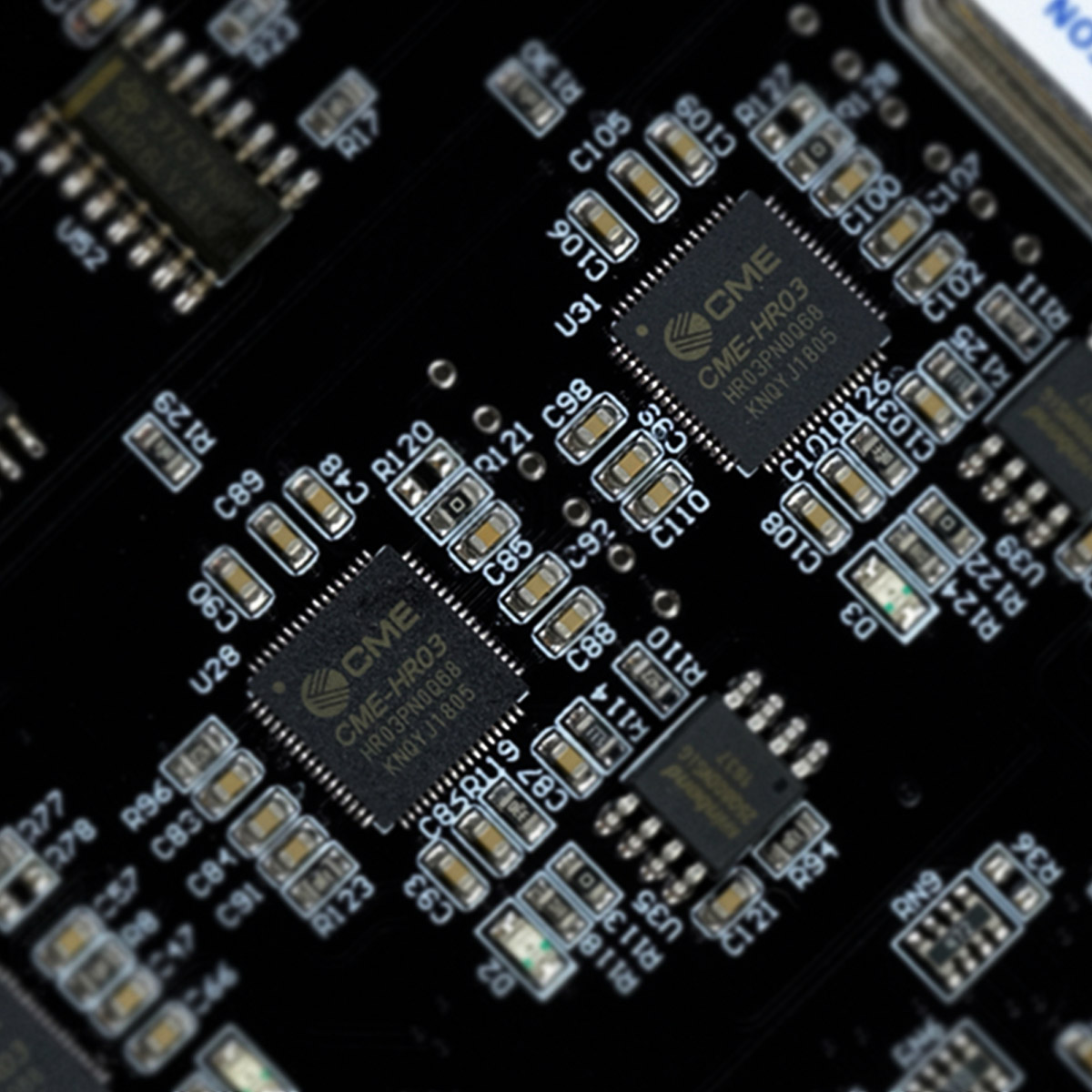

In addition, in order to offer the lowest possible jitter level, the Gustard U16 has no less than 3 FPGAs allowing signal synchronization and managing the WCK 10M output circuit.

At the heart of the USB circuit, an FPGA is used to operate the USB interface in slave mode. Thus, the latter receives the clock signal generated by the FPGA clock management system and outputs only the audio data, limiting the interference generated.

The Gustard U16 also has a 10M CLK input. It is therefore possible to use a very high quality external clock to further improve the performance of the interface.

For safety reasons, the Gustard U16 does not automatically switch to the external clock if it is connected. It is necessary to manually select the internal and external clock sources.

Accusilicon AS318-B Clocks

The internal clock signal is generated by a pair of Accusilicon AS318-B ultra-low phase noise femtosecond clocks. These provide a jitter of only 88 femtoseconds (10Hz-1MHz). In addition, the U16 includes a multifunctional BNC output that can output a S/PDIF or WCK signal.

Regulated linear power supply

The Gustard U16 incorporates a regulated linear power supply based on the use of a toroidal transformer specially designed for audio applications. This optimized power supply stage provides the entire circuit with a clean power supply at the lowest possible noise level.

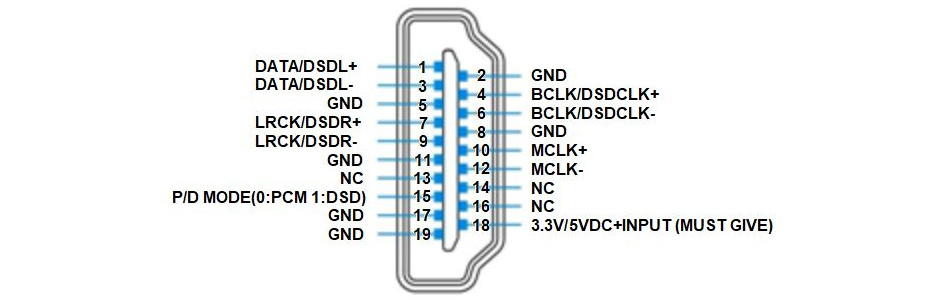

I2S HDMI LVDS Pinout

Technical characteristics

| Specifications | |

|---|---|

| Product type | Digital interface |

| Inputs | 1x USB-B 1x BNC 10M 50Ω (0-16dBm) |

| Outputs | 1x Coaxial S/PDIF 75Ω 1x XLR AES3 110Ω 1x Optical Toslink 1x Multi-function BNC 75Ω 1x I2S HDMI LVDS |

| Outputs level | Coaxial S/PDIF : 500mVpp @ 75Ω XLR AES3 : 2.1Vpp @ 110Ω BNC S/PDIF : 750mVpp @ 75Ω BNC WCK : 3.3Vpp max. |

| Supported sampling rates | I2S HDMI LVDS : PCM up to 32bit 768kHz / DSD up to DSD512 Coaxial SPDIF : PCM up to 24bit 384kHz / DoP64-128 XLR AES3 : PCM up to 24bit 384kHz / DoP64-128 Optical Toslink : PCM up to 24bit 192kHz / DoP64 BNC SPDIF : PCM up to 24bit 384kHz / DoP64-128 |

| WCK clock output frequency | PCM 44.1-768kHz / DSD 2.82M-22.57M |

| Compatibility | Windows 7 (SP1 or later) / 8 / 10 with driver Mac OS Linux |

| Integrated clocks | 2x Accusilicon AS318-B |

| FPGA | 3x CME-HR03 |

| General | |

|---|---|

| Consumption | < 15W |

| Case material | Sandblasted Aluminium |

| Dimensions (LxPxH) | 220 x 170 x 50mm |

| Color | Black |

| Input | BNC |

| Output | Optical Toslink |

| Output | XLR |

| Output | BNC |

| Output | I2S LVDS via HDMI |

| Output | Coaxial SPDIF |

| Max sampling rate | 384kHz |

| Max sampling rate | DSD512 |

| Color | Black |

| Interface chip | ES8620 |

Average votes 5.0 / 5 2 reviews | Why write products reviews ? You can share your feelings about products and help other people by sharing your experience |

Philippe P.

Dès son installation l'interface GUSTARD U16 a fait faire un bond en avant à mon système . Une électronique bien faite dans un boîtier à la finition exemplaire, une connectique complète et de qualité. Tout ça pour une musicalité pur plaisir. Prix très contenu, comme toujours avec AUDIOPHONICS. Bravo!

Christian G.

Cette interface numérique s'avère efficace et la liaison USB convertie en AES/EBU est tout simplement excellente. Mon DAC a gagné en musicalité. J'avais besoin de cette interface car j'utilise un DAC qui ne possède pas de liaison USB mais seulement des liaisons toslink , coaxiale et XLR AES/UBU. Cette interface apporte vraiment un grand plus sur le message musicale.